Student teams earn prizes for analog-digital converter circuit designs in EECS 511

The winning projects were designed for battery-operated mobile applications as well as instrumentation and measure applications.

Students in the graduate level course, Integrated Analog/Digital Interface Circuits (EECS 511), taught by Prof. Michael Flynn, competed for cash prizes while presenting their final design projects thanks to the support of Analog Devices, Inc. Two winning projects and teams were determined by an expert panel at Analog Devices.

Enlarge

Enlarge

1st place – $1500 prize

A 560µW Dynamic Zoom-ADC with 90.7dB SNDR for Audio Applications, by Huajun Zhang, Li Xu, Zhehong Wang, and Milad Moosavifar

Enlarge

Enlarge

Audio applications like noise cancellation and audio codecs require high signal-to-(noise and distortion) (SNDR) and dynamic range (DR) performance for their ADCs. Traditional implemenations use Σ∆ modulators to address this because of their high resolution, but these require a high oversampling ratio (OSR) and a high-order loop filter to suppress quantization noise and have a limited stable input range. Multi-bit quantizers, which alleviate this problem, are usually implemented with flash ADCs, but their power consumption scales exponentially with resolution.

In contrast, successive approximation register (SAR) ADCs have been gaining popularity because of their highly digital nature and excellent energy efficiency, especially for low-to-medium-resolution applications. For very-low-frequency inputs, the incremental zoom ADC was proposed to take advantage of both ADC architectures, where the conversion is finished in two steps. In this work, the group implemented a dynamic zoom ADC with asynchronous SAR, where the Σ∆ reference voltages can be updated more promptly without the need of an additional high-frequency clock. The group also used merged capacitor switching (MCS) to further reduce the SAR ADC’s power consumption.

Enlarge

Enlarge

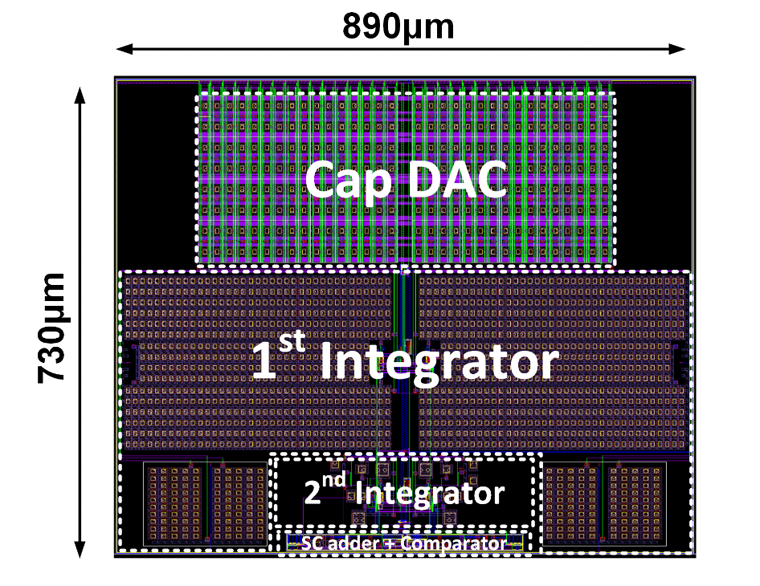

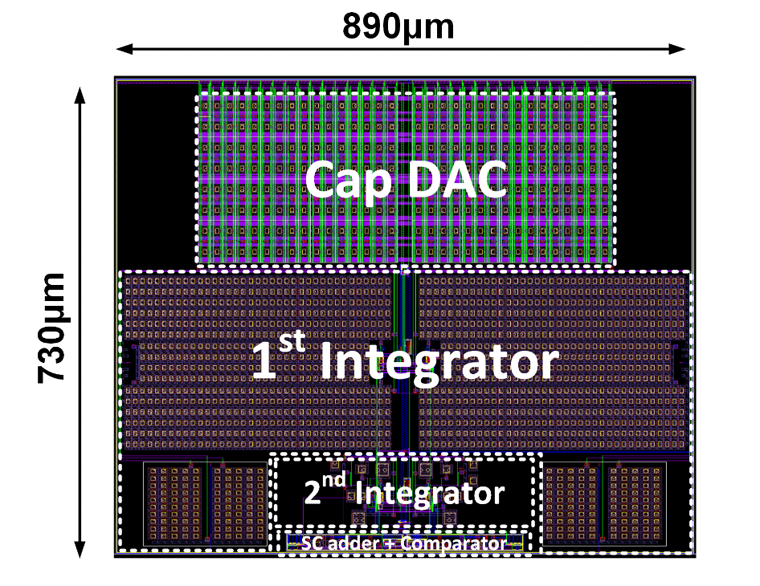

2nd place – $500 prize

A 38 µW 19.1-bit incremental Zoom ADC with 2.2 V input range, by Hyunsoo Song, Taewook Kang, Teyuh Chou, and Wootaek Lim

Enlarge

Enlarge

In instrumentation applications, ADCs that have high absolute accuracy, high linearity, and low offset and noise are often required. Incremental data converters (IDCs) have properties that are well matched to the instrumentation and measurement applications. These converters show high linearity, low offset, and also less conversion time.

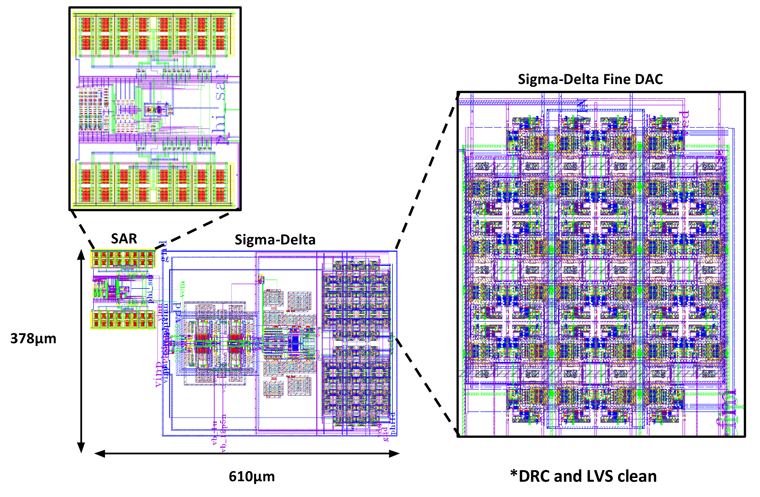

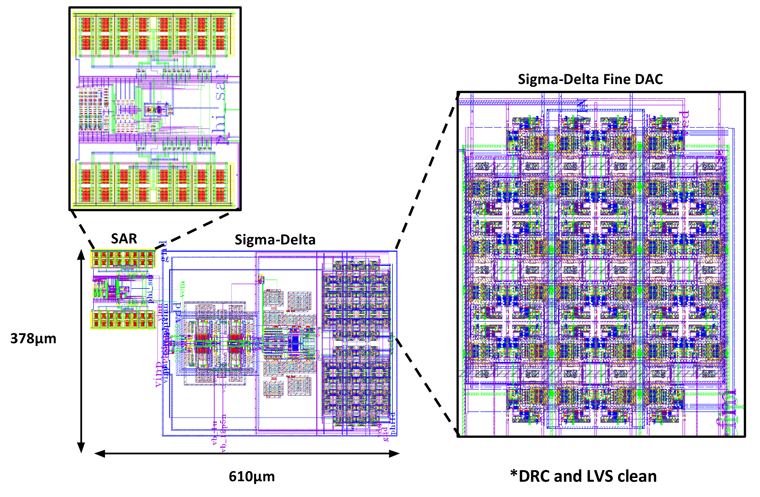

This paper implements an incremental zoom-ADC that combines a coarse 6-bit successive approximation register (SAR) conversion with a fine 13-bit ΔΣ conversion. In contrast to the conventional two-step architecture ADCs, the fine converter of a proposed zoom ADC does not digitize the residue of the coarse converter, and therefore the accuracy of the conversion is dictated by the accuracy of the fine converter.

MENU

MENU